Datasheet

# **Features and Benefits**

- Linear Hall Effect Sensor IC

- On Chip Signal Processing for Robust and Accurate Sensing

- Programmable Measurement Range

- Programmable Linear Transfer Characteristic (4 or 8 Multi-points or 16 or 32 Piece-Wise-Linear)

- Selectable Short PWM Code (SPC) or Analog Output modes

- SAE J2716 APR2016 SENT

- ISO26262 CSIL READY

ASIL-C Safety Element out of Context for SPC output, ASIL-B Safety Element out of Context capable for analog output

- 48-bit programmable ID Number

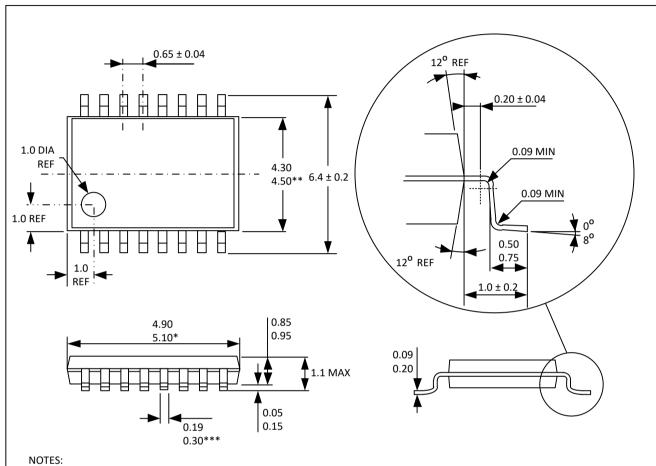

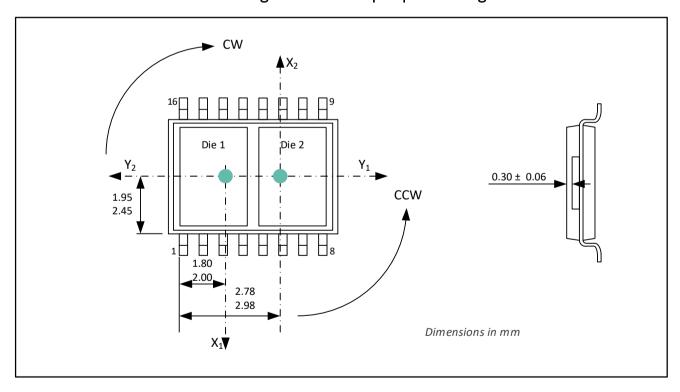

- Dual Die (Full Redundant) TSSOP-16 package RoHS Compliant

- AEC Q-100 Grade 0 qualified

TSSOP-16

# **Application Examples**

- Steering Torque Sensor

- Acceleration, Brake, or Clutch Sensor

- Absolute Linear Position Sensor

- Float-Level Sensor

- Non-Contacting Potentiometer

- Small Angle Position Sensor

- Small Stroke Position Sensor

# **Description**

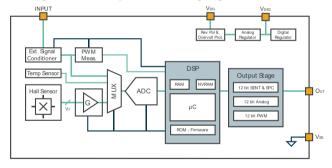

The MLX91377 is a monolithic magnetic position processor IC. It consists of a Hall effect magnetic front end, an analog to digital signal conditioner, a DSP for advanced signal processing and an output stage driver.

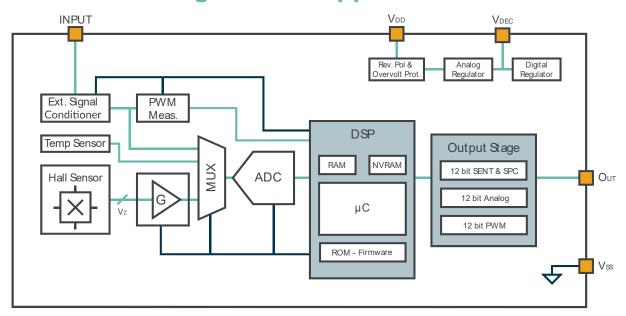

The MLX91377 is sensitive to the magnetic flux density applied perpendicular to the IC (i.e. Bz). This allows the MLX91377 with the correct magnetic circuit to decode the absolute position of any moving magnet or linear displacement, see Figure 2). It enables the design of non-contacting position sensors that are frequently required for both automotive and industrial applications.

The MLX91377 provides two output modes. Firstly, the IC supports SPC frames encoded according to a Secure Sensor format. Through programming, the MLX91377 can also be configured to output an analog signal.

# **Ordering Information**

| Product  | Temperature | Package | Option Code | Packing<br>Form | Definition                                         |

|----------|-------------|---------|-------------|-----------------|----------------------------------------------------|

| MLX91377 | G           | GO      | ADB-080     | RE              | SPC output, TSSOP-16 dual-die package              |

| MLX91377 | G           | GO      | ADB-010     | RE              | High speed analog output, TSSOP-16 dualdie package |

Table 1 - Ordering Codes

| Temperature Code:           | G: from -40°C to 160°C                                                                                   |  |  |  |  |  |

|-----------------------------|----------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Package Code:               | GO: TSSOP-16 package                                                                                     |  |  |  |  |  |

|                             |                                                                                                          |  |  |  |  |  |

| Option Code - Chip revision | ADB-123 : Chip Revision                                                                                  |  |  |  |  |  |

|                             | <ul> <li>ADB : Standard preferred revision</li> </ul>                                                    |  |  |  |  |  |

| Option Code - Application   | ADB-123: 1-Application - Magnetic configuration                                                          |  |  |  |  |  |

|                             | 0: Linear Hall                                                                                           |  |  |  |  |  |

| Option Code - SW            | ADB-123: 2-SW configuration: output mode, protocol                                                       |  |  |  |  |  |

| configuration: output       | <ul><li>1: high speed analog output mode</li></ul>                                                       |  |  |  |  |  |

| mode, protocol              | <ul> <li>8: SPC output mode, 1.5μs tick time</li> </ul>                                                  |  |  |  |  |  |

| Option Code - TSSOP-16      | ADB-123: 3-TSSOP-16 package configuration                                                                |  |  |  |  |  |

| package configuration       | <ul><li>0: TSSOP-16 dual-die package</li></ul>                                                           |  |  |  |  |  |

| Packing Form:               | -RE : Tape & Reel                                                                                        |  |  |  |  |  |

|                             | GO: 4500 pcs/reel                                                                                        |  |  |  |  |  |

| Ordering Example:           | MLX91377GGO-ADB-080-RE                                                                                   |  |  |  |  |  |

|                             | For a linear hall sensor with SPC protocol in TSSOP-16 dual-die package, delivered on a Reel of 4500pcs. |  |  |  |  |  |

Table 2 - Ordering Codes Information

**REVISION 001 - 27-Feb-2020** Page 2 of 58

# **Contents**

| Features and Benefits                                     | 1  |

|-----------------------------------------------------------|----|

| Application Examples                                      | 1  |

| Description                                               | 1  |

| Ordering Information                                      | 2  |

| Functional Diagram and Application Modes                  | 5  |

| 2. Glossary of Terms                                      | 6  |

| 3. Pin Definitions and Descriptions                       | 7  |

| 3.1. Pin Definition for TSSOP-16 Dual-Die package         | 7  |

| 4. Absolute Maximum Ratings                               | 8  |

| 5. Isolation Specification                                | 8  |

| 6. General Electrical Specifications                      | 9  |

| 7. Timing Specification                                   | 11 |

| 7.1. General Timing Specifications                        | 11 |

| 7.2. Timing Definitions                                   | 12 |

| 7.3. Analog Output Timing Specification                   | 12 |

| 7.4. SPC Timing Specifications                            | 13 |

| 8. Accuracy Specifications                                | 15 |

| 8.1. Definitions                                          | 15 |

| 8.2. Magnetic Field Specification for the Sensor Accuracy | 16 |

| 8.3. Accuracy Specifications                              | 16 |

| 9. Memory Specifications                                  | 18 |

| 10. Output Characteristic and Accuracy                    | 19 |

| 10.1. Analog Output                                       | 19 |

| 10.2. Digital Output                                      | 19 |

| 11. End-User Programmable Items                           | 27 |

| 12. End-User Identification Items                         | 32 |

| 13. Description of End-User Programmable Items            | 33 |

| 13.1. Output modes                                        | 33 |

| 13.2. Sensor Front-End                                    | 35 |

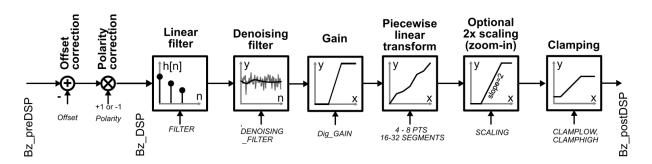

| 13.3. Sensor DSP Configuration                            | 35 |

| 13.4. Filtering                                           | 43 |

| 13.5. Programmable Diagnostics Settings                   | 44 |

| 14. Functional Safety                                     | 46 |

#### Datasheet

| 14.1. Safety Manual                                                                     | 46                           |

|-----------------------------------------------------------------------------------------|------------------------------|

| 14.2. Safety Mechanisms                                                                 | 46                           |

| 14.3. Fault Handling Time Interval                                                      | 50                           |

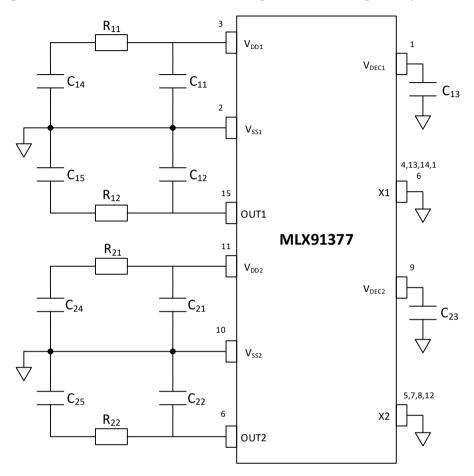

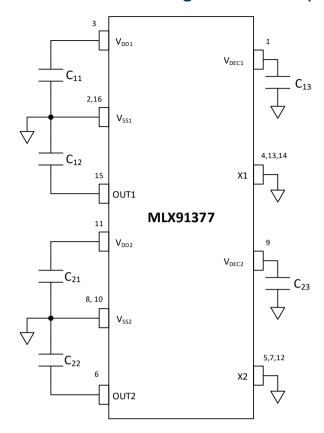

| 15. Recommended Application Diagrams                                                    | 52                           |

| 15.1. Wiring in TSSOP-16 dual-die Package for Analog Output                             | 52                           |

| 15.2. Wiring in TSSOP-16 dual-die Package for SPC Output                                | 53                           |

| 16. Standard Information Regarding Manufacturability of Melexis Products with Different |                              |

| Soldering Processes                                                                     | 54                           |

| Soldering Processes                                                                     |                              |

| -                                                                                       | 54                           |

| 17. ESD Precautions                                                                     | 54<br>55                     |

| 17. ESD Precautions                                                                     | <b>54</b><br><b>55</b><br>55 |

| 17. ESD Precautions                                                                     | <b>54</b><br><b>55</b><br>55 |

# 1. Functional Diagram and Application Modes

Figure 1 - MLX91377 Block diagram

### **Linear Motion**

Figure 2 - Application Modes

**REVISION 001 - 27-Feb-2020** Page 5 of 58

# 2. Glossary of Terms

| Name      | Description                                                      |

|-----------|------------------------------------------------------------------|

| ADC       | Analog-to-Digital Converter                                      |

| AoU       | Assumption of Use                                                |

| ASP       | Analog Signal Processing                                         |

| AWD       | Absolute Watchdog                                                |

| CPU       | Central Processing Unit                                          |

| CRC       | Cyclic Redundancy Check                                          |

| DC        | Duty Cycle of the output signal i.e. $T_{ON}/(T_{ON} + T_{OFF})$ |

| DMP       | Dual Mold Package                                                |

| DP        | Discontinuity Point                                              |

| DSP       | Digital Signal Processing                                        |

| DTI       | Diagnostic Test Interval                                         |

| ECC       | Error Correcting Code                                            |

| EMA       | Exponential Moving Average                                       |

| EMC       | Electro-Magnetic Compatibility                                   |

| EoL       | End of Line                                                      |

| FIR       | Finite Impulse Response                                          |

| FHTI      | Fault Handling Time Interval                                     |

| Gauss (G) | Alternative unit for the magnetic flux density (10G = 1mT)       |

| HW        | Hardware                                                         |

| IMC       | Integrated Magnetic Concentrator                                 |

| Name      | Description                                           |  |  |  |  |  |  |  |

|-----------|-------------------------------------------------------|--|--|--|--|--|--|--|

| INL/DNL   | Integral Non-Linearity / Differential Non-Linearity   |  |  |  |  |  |  |  |

| IWD       | Intelligent Watchdog                                  |  |  |  |  |  |  |  |

| LNR       | Linearization                                         |  |  |  |  |  |  |  |

| LSB/MSB   | Least Significant Bit / Most Significant Bit          |  |  |  |  |  |  |  |

| NC        | Not Connected                                         |  |  |  |  |  |  |  |

| NVRAM     | Non Volatile RAM                                      |  |  |  |  |  |  |  |

| POR       | Power On Reset                                        |  |  |  |  |  |  |  |

| PSF       | Product Specific Functions                            |  |  |  |  |  |  |  |

| PWL       | Piecewise Linear                                      |  |  |  |  |  |  |  |

| PWM       | Pulse Width Modulation                                |  |  |  |  |  |  |  |

| RAM       | Random Access Memory                                  |  |  |  |  |  |  |  |

| ROM       | Read-Only Memory                                      |  |  |  |  |  |  |  |

| SPC       | Short PWM code                                        |  |  |  |  |  |  |  |

| SCN       | Status & Communication Nibble                         |  |  |  |  |  |  |  |

| SEooC     | Safety Element out of Context                         |  |  |  |  |  |  |  |

| тс        | Temperature Coefficient (in ppm/°C)                   |  |  |  |  |  |  |  |

| Tesla (T) | SI derived unit for the magnetic flux density (Vs/m2) |  |  |  |  |  |  |  |

Table 3 - Glossary of Terms

**REVISION 001 - 27-Feb-2020** Page 6 of 58

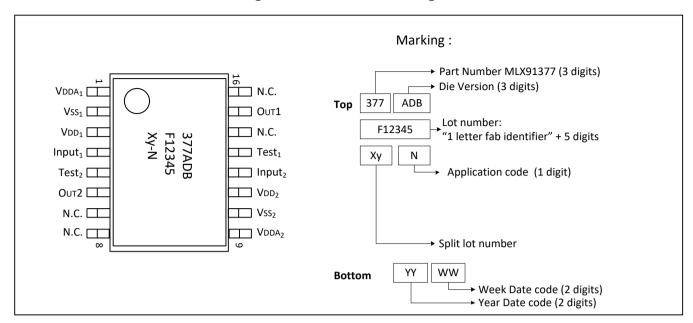

# 3. Pin Definitions and Descriptions

# 3.1. Pin Definition for TSSOP-16 Dual-Die package

| Pin # | Name               | Description         |

|-------|--------------------|---------------------|

| 1     | V <sub>DEC1</sub>  | Decoupling pin die1 |

| 2     | $V_{SS1}$          | Ground die1         |

| 3     | $V_{\mathtt{DD1}}$ | Supply die1         |

| 4     | Input₁             | For test            |

| 5     | Test <sub>2</sub>  | For test            |

| 6     | OUT <sub>2</sub>   | Output die2         |

| 7     | N.C.               | Not connected       |

| 8     | N.C.               | Not connected       |

| 9     | $V_{DEC2}$         | Decoupling pin die2 |

| 10    | $V_{SS2}$          | Ground die2         |

| 11    | $V_{DD2}$          | Supply die2         |

| 12    | Input <sub>2</sub> | For test            |

| 13    | Test₁              | For test            |

| 14    | N.C.               | Not connected       |

| 15    | OUT <sub>1</sub>   | Output die1         |

| 16    | N.C.               | Not connected       |

Table 4 - TSSOP-16 dual-die package pin definition and description

Pins Input and Test are internally grounded. For optimal EMC behaviour always connect the unused pins to the ground of the PCB.

**REVISION 001 - 27-Feb-2020** Page 7 of 58

Page 8 of 58

# 4. Absolute Maximum Ratings

| Parameter                                 | Symbol               | Min        | Тур | Max      | Unit | Condition      |

|-------------------------------------------|----------------------|------------|-----|----------|------|----------------|

| Supply Voltage <sup>(1)</sup>             | $V_{\text{DD}}$      |            |     | 28<br>37 | V    | < 48h<br>< 60s |

| Reverse Voltage Protection <sup>(1)</sup> | $V_{DD-rev}$         | -14<br>-18 |     |          | V    | < 48h<br>< 1h  |

| Positive Output Voltage <sup>(1)</sup>    | $V_{OUT}$            |            |     | 28       | ٧    | < 48h          |

| Reverse Output Voltage <sup>(1)</sup>     | $V_{OUT-rev}$        | -14<br>-18 |     |          | V    | < 48h<br>< 1h  |

| Internal Voltage                          | $V_{DEC}$            |            |     | 3.6      | V    |                |

|                                           | $V_{DEC\text{-rev}}$ | -0.3       |     |          | V    |                |

| Positive Input pin Voltage                | $V_{Input}$          |            |     | 6        | V    |                |

| Reverse Input pin Voltage                 | $V_{Input-rev}$      | -3         |     |          | V    |                |

| Operating Temperature                     | $T_{AMB}$            | -40        |     | +160     | °C   |                |

| Junction Temperature                      | TJ                   |            |     | +175     | °C   |                |

| Storage Temperature                       | $T_{ST}$             | -55        |     | +170     | °C   |                |

| Magnetic Flux Density                     | $B_{\text{max}}$     | -1         |     | 1        | Т    |                |

Table 5 - Absolute maximum ratings

Exceeding any of the absolute maximum ratings may cause permanent damage.

Exposure to absolute maximum ratings conditions for extended periods may affect device reliability.

# 5. Isolation Specification

Only valid for the TSSOP-16 package dual die version (code GO).

| Parameter            | Symbol            | Min | Тур | Max | Unit | Condition                                                               |

|----------------------|-------------------|-----|-----|-----|------|-------------------------------------------------------------------------|

| Isolation Resistance | R <sub>isol</sub> | 4   | -   | -   | МΩ   | Between dice, measured between $V_{SS1}$ and $V_{SS2}$ with +/-20V bias |

Table 6 - Isolation specification

REVISION 001 - 27-Feb-2020

<sup>&</sup>lt;sup>1</sup> Valid for full operating temperature range

# 6. General Electrical Specifications

General electrical specifications are valid for temperature range [-40; 160] °C and supply voltage range [4.5; 5.5] V unless otherwise noted.

| Electrical<br>Parameter               | Symbol                 | Min              | Тур               | Max             | Unit       | Condition                                                                                                                |

|---------------------------------------|------------------------|------------------|-------------------|-----------------|------------|--------------------------------------------------------------------------------------------------------------------------|

| Supply Voltage                        | $V_{DD}$               | 4.5              | 5                 | 5.5             | V          | For regulator                                                                                                            |

| Supply Current <sup>(2)</sup>         | I <sub>DD</sub>        | 9                | 11                | 13.5            | mA         | Analog/SPC output                                                                                                        |

| Start-up Level (rising)               | $V_{DDstartH}$         | 3.95             | 4.1               | 4.25            | V          |                                                                                                                          |

| Start-up Hysteresis                   | $V_{DDstartHyst}$      | -                | 200               | -               | mV         |                                                                                                                          |

| PTC Entry Level (rising)              | V <sub>PROV0</sub> (3) | 6.30             | 6.55              | 6.80            | V          |                                                                                                                          |

| PTC Entry Level<br>Hysteresis         | V <sub>PROV0Hyst</sub> | 400              | 500               | 600             | mV         |                                                                                                                          |

| Output Short<br>Circuit Current       | louTshort              | -35<br>10        |                   | -10<br>35       | mA         | Vout = 0 V<br>Vout = 5 V                                                                                                 |

|                                       |                        | 5                | 10                |                 | kΩ         | Analog pull-up/ down                                                                                                     |

| Output Load                           | $R_L$                  | 3                | -                 | 55              | kΩ         | Push-pull and improved emission modes (4)                                                                                |

|                                       |                        | 1                | -                 | 100             | kΩ         | Open drain pull-up/down(4)                                                                                               |

| Digital open drain                    | $V_{satLoOd}$          | 0                |                   | 10              | $%V_{ext}$ | Pull-up to any external voltage $V_{ext} \le 18V$ , $I_L \le 3.4mA$                                                      |

| Digital open drain output level       | $V_{satHiOd}$          | 90               |                   | 100             | %VDD       | Pull-down to GND with any supply voltage $V_{DD} \le 18V$ , $I_L \le 3.4mA$                                              |

| Digital output Ron                    | $R_{on}$               | 27               | 50                | 100             | Ω          | Push-pull mode                                                                                                           |

| Analog Saturation<br>Output Level (5) | $V_{satA\_lo}$         |                  | 0.5<br>3.3<br>2.3 | 1.2<br>7.4<br>5 | %VDD       | Pull-up load $R_L \ge 10~k\Omega$ to 5 V Pull-up load $R_L \ge 5~k\Omega$ to 18 V Pull-up load $R_L \ge 2k\Omega$ to 5 V |

|                                       | $V_{satA\_hi}$         | 97<br>95<br>87.5 | 99<br>98<br>96    |                 | %VDD       | Pull-down load $R_L \geq 10~k\Omega$ Pull-down load $R_L \geq 5~k\Omega$ Pull-down load $R_L \geq 2~k\Omega$             |

\_

<sup>&</sup>lt;sup>2</sup> The chip can also be configured to have lower current consumption, at the cost of speed. Contact Melexis for more details

<sup>&</sup>lt;sup>3</sup> Programming through Connector (PTC) requires raising supply voltage above Vprov0 or Vprov1. This is customer configurable by setting a bit in the NVRAM

<sup>&</sup>lt;sup>4</sup> Output resistance should be selected together with the output capacitive load to correspondingly match the application, i.e. tick time, SPC ID, to allow appropriate time window for the trigger pulse reception. More details see section 10.2.3.

<sup>&</sup>lt;sup>5</sup> For analog output, see section 13.1.1.

| Electrical<br>Parameter                     | Symbol           | Min                | Тур               | Max             | Unit | Condition                                                                                                                 |

|---------------------------------------------|------------------|--------------------|-------------------|-----------------|------|---------------------------------------------------------------------------------------------------------------------------|

| Digital Output                              | $V_{satD\_lopp}$ |                    |                   | 0.2<br>0.5      | V    | Pull-up load $R_L \ge 10 \ k\Omega$<br>Pull-up load $10 \ k\Omega > R_L \ge 5 \ k\Omega$                                  |

| Level in push-pull<br>mode <sup>(6)</sup>   | $V_{satD\_hipp}$ | VDD-0.2<br>VDD-0.5 |                   |                 | V    | Pull-down load $R_L \ge 10~k\Omega$<br>Pull-down load $10~k\Omega > R_L \ge 5~k\Omega$                                    |

| Digital Output<br>Level in improved         | $V_{satD\_loie}$ |                    |                   | 0.5             | V    | Pull-up load $R_L \geq 10~k\Omega$                                                                                        |

| emission mode (6)                           | $V_{satD\_hiie}$ | 4.1                |                   |                 | V    | Pull-down load $R_L \geq 10~k\Omega$                                                                                      |

| Active Diagnostic                           | Diag_lo          |                    | 0.5<br>3.3<br>2.3 | 1.2<br>7.4<br>5 | %VDD | Pull-up load $R_L \ge 10~k\Omega$ to 5 V Pull-up load $R_L \ge 5~k\Omega$ to 18 V Pull-up load $R_L \ge 2~k\Omega$ to 5 V |

| Output Level                                | Diag_hi          | 97<br>95<br>87.5   | 99<br>98<br>96    |                 | %VDD | Pull-down load $R_L \ge 10~k\Omega$ Pull-down load $R_L \ge 5~k\Omega$ Pull-down load $R_L \ge 2~k\Omega$                 |

| Passive Diagnostic<br>Output Level          | BVssPD           |                    | 2.5<br>1          | 4<br>1.6        | %VDD | Pull-down load $R_L \le 25 \text{ k}\Omega$<br>Pull-down load $R_L \le 10 \text{ k}\Omega$                                |

| Vss Broken-Wire<br>Detection <sup>(7)</sup> | BVssPU           | 99.5               | 100               |                 | %VDD | Pull-up load $R_L \geq 1~k\Omega$                                                                                         |

| Passive Diagnostic                          | BVddPD           |                    | 0                 | 0.5             | %VDD | Pull-down load $R_L \geq 1 \; k\Omega$                                                                                    |

| Output Level VDD Broken-Wire Detection (7)  | BVDDPU           | 92.5<br>97         | 97.5<br>99        |                 | %VDD | Pull-up load $R_L \le 25 \text{ k}\Omega$<br>Pull-up load $R_L \le 10 \text{ k}\Omega$                                    |

Table 7 – Electrical Specifications

**REVISION 001 - 27-Feb-2020** Page 10 of 58

<sup>&</sup>lt;sup>6</sup> See section 13.1.1.

<sup>&</sup>lt;sup>7</sup> Valid for dual-die configuration as well, i.e. TSSOP-16 package, where the two dies have the same supply and ground level, while the output of one die is connected with PU and the output of the other one is connected with PD. For detailed information, see also section 14.2.

# 7. Timing Specification

Timing specifications are valid for temperature range [-40; 160] °C and supply voltage range [4.5; 5.5] V unless otherwise noted.

# 7.1. General Timing Specifications

| Parameter                             | Symbol               | Min  | Тур | Max  | Unit                | Condition                                                                                                                                           |

|---------------------------------------|----------------------|------|-----|------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Main Clock Frequency                  | F <sub>CK</sub>      | 22.8 | 24  | 25.2 | MHz                 | Including thermal and lifetime drift                                                                                                                |

| Main Clock Frequency<br>Thermal Drift | $\Delta F_{CK,T}$    | -2.5 | -   | 2.5  | %F <sub>ck</sub>    | Relative to 35°C                                                                                                                                    |

| Main Clock Frequency<br>Total Drift   | $\Delta F_{CK, TOT}$ | -3.5 | -   | 3.5  | %F <sub>ck</sub>    | Relative to 35°C after factory trimming at Melexis, including thermal and lifetime drift                                                            |

| 1MHz Clock Frequency                  | F <sub>1M</sub>      |      | 1   |      | MHz                 |                                                                                                                                                     |

| Intelligent Watchdog<br>Timeout       | $T_IWD$              |      | 4   | (8)  | ms                  | F <sub>CK</sub> = 24MHz                                                                                                                             |

| Absolute Watchdog<br>Timeout          | $T_AWD$              |      | 2.7 | (8)  | ms                  | F <sub>1M</sub> = 1MHz                                                                                                                              |

| Analog Diagnostics                    |                      |      |     | 3    | ms                  | Diagnostics response time, detailed description see section 14.2, Table 40, for analog output                                                       |

| Test Interval (9)                     | DTI <sub>ANA</sub>   |      |     | 9    | SPC<br>trigger<br>s | Diagnostics response time, detailed description see section 14.2, Table 40, for SPC output, e.g. with 500µs ECU frame time, the max. value is 4.5ms |

| Digital Diagnostics                   |                      |      |     | 4.5  | ms                  | Diagnostics response time, detailed description see section 14.2, Table 40, for analog output                                                       |

| Test Interval (9)                     | DTI <sub>DIG</sub>   |      |     | 9    | SPC<br>trigger<br>s | Diagnostics response time, detailed description see section 14.2, Table 40, for SPC output, e.g. with 500µs ECU frame time, the max. value is 4.5ms |

Table 8 - General Timing Specifications

**REVISION 001 - 27-Feb-2020** Page 11 of 58

<sup>&</sup>lt;sup>8</sup> Maximum value is defined by the clock frequency tolerance, see parameter "Main Clock frequency".

<sup>&</sup>lt;sup>9</sup> Only the Diagnostics response time is specified. The fault tolerance time interval (FTTI) should take into account the response time of the ECU additionally, i.e. on the item level, which is independent of the MLX91377.

### 7.2. Timing Definitions

#### 7.2.1. Startup Time

In SPC mode, during startup, the sensor transmits frames with status bit defined by the parameter SPC\_SCN\_INIT, until it is able to transmit valid magnetic measurements. These initialisation frames content can be chosen by user with the parameter SENT\_INIT\_GM (see chapter 11 for more detail).

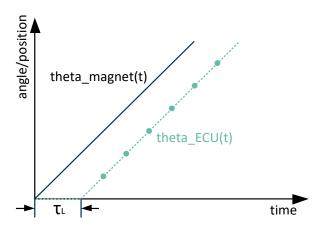

#### 7.2.2. Latency (average)

Latency is the average lag between the movement of the detected object (magnet) and the response of the sensor output, as shown in Figure 3, where theta\_ECU(t) is sampled as the beginning of the synchronization pulse. This value is representative of the time constant of the system for regulation calculations.

Figure 3 - Definition of Latency

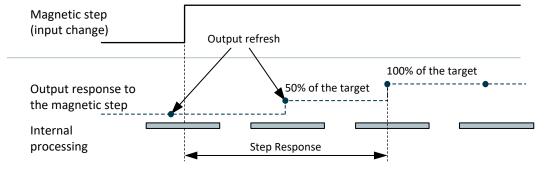

#### 7.2.3. Step Response (worst case)

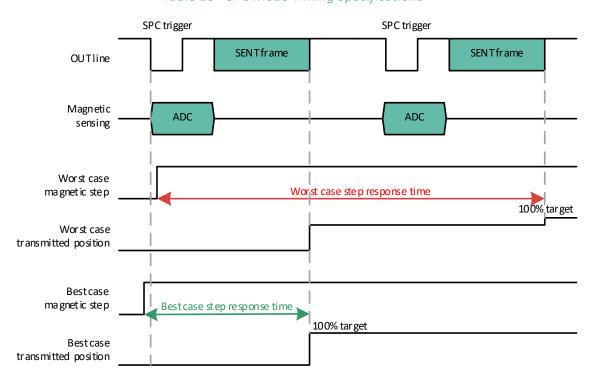

The step response is a suitable metric for the "delay" of the sensor in case of an abrupt step in the magnetic change, considering 100% settling time without any DSP filter. Full settling is typically achieved in just two steps. The sensor is asynchronous with the magnetic step change: the 100% settling time will fall in a time window; worst case is illustrated in the figure below.

Figure 4 - Step Response Definition

Figure 4 is not valid for the SPC output, since the output is depending on the trigger pulse. The definition of the step response in SPC mode is clarified in Table 10.

# 7.3. Analog Output Timing Specification

For the analog output configurations, specifications are valid under the corresponding minimum and typical conditions defined in section 6. The timing specifications are listed in Table 9.

**REVISION 001 - 27-Feb-2020** Page 12 of 58

| Parameter             | Symbol                        | Min | Тур        | Max | Unit | Condition                                                            |

|-----------------------|-------------------------------|-----|------------|-----|------|----------------------------------------------------------------------|

| Output refresh period | $\tau_{\text{R}}$             |     | 160        |     | μs   |                                                                      |

| Latency               | $\tau_{\scriptscriptstyle L}$ |     | 70         |     | μs   | no external load                                                     |

| Step response         | $\tau_{\scriptscriptstyle S}$ |     |            | 250 | μs   | no external load                                                     |

| Start-up time         | $	au_{SU}$                    |     | 3.2        |     | ms   |                                                                      |

| Slew Rate             | SR                            |     | 120<br>200 |     | V/ms | capacitive load at output is 100nF capacitive load at output is 10nF |

Table 9 - Analog General Timing Specifications

### 7.4. SPC Timing Specifications

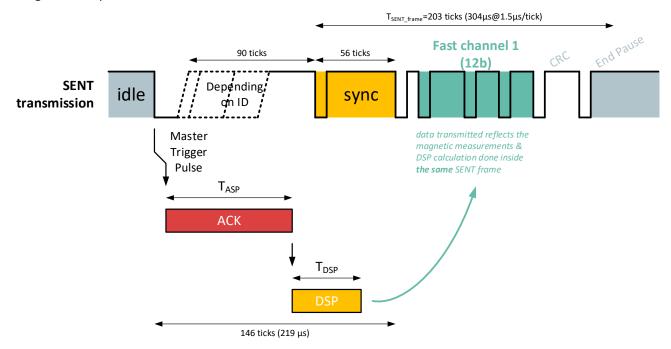

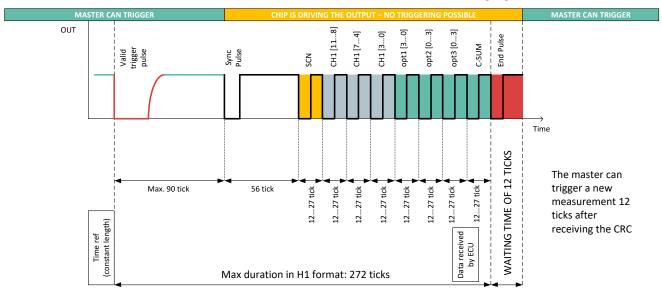

In SPC mode, the MLX91377 starts data acquisition once the trigger pulse has been received, regardless of the configured mode. It will send the acquired data in the same SENT frame. This feature is available for any tick time greater than or equal to  $1.5\mu s$ . Please check the section 10.2 for more details on the configuration options.

Figure 5 – SPC timing illustration in 1.5µs tick time mode and H.2 format

| Parameter                                           | Symbol        | Min | Тур | Max | Unit | Condition                                              |

|-----------------------------------------------------|---------------|-----|-----|-----|------|--------------------------------------------------------|

| Time between trigger received & acquisition started | $T_{tr2acq}$  |     | 10  | (8) | μs   | Tick: 1.5 μs  SPC_RX_FILT_TIME (10): 6  SPC_TRIG_TH: 0 |

| Startup time (ability to                            | $T_{stupspc}$ |     | 3.5 | 3.9 | ms   |                                                        |

<sup>&</sup>lt;sup>10</sup> SPC\_RX\_FILT\_TIME is the parameter for the SPC trigger pulse filtering. Its unit is tick time. It must be aligned with the longest NIBBLE low time on the bus, in order to separate SENT pulses from SPC trigger pulses (NIBBLE\_PULSE\_FIXED[]).

**REVISION 001 - 27-Feb-2020** Page 13 of 58

| Parameter                                  | Symbol       | Min  | Тур  | Max  | Unit | Condition                                                                                                                                                                                                                      |

|--------------------------------------------|--------------|------|------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| receive the 1 <sup>st</sup> trigger pulse) |              |      |      |      |      |                                                                                                                                                                                                                                |

| Latency                                    | $T_{latcy}$  |      | 450  |      | μs   |                                                                                                                                                                                                                                |

| Step Response (worst case)                 | $T_{wcStep}$ |      |      | 1    | ms   | The worst-case step response time is equal to twice a SPC trigger plus its SENT response time, when the field change happens right after the trigger pulse, see Figure 6. It is then 1 ms if the SPC trigger period is 0.5 ms. |

| Jitter between the acquisition             | $J_{acq}$    |      |      | 5    | μs   |                                                                                                                                                                                                                                |

| Inter-die synchronicity                    |              | 8.45 | 9.08 | 9.71 | μs   | The absolute time difference of the magnetic information acquisition between the two dice in bus transmission mode, see section 0, based on 1.5 µs tick time                                                                   |

Table 10 - SPC Mode Timing Specifications

Figure 6 – Illustration of the best and worst case step response in SPC mode

**REVISION 001 - 27-Feb-2020** Page 14 of 58

Datasheet

# 8. Accuracy Specifications

Accuracy specifications are valid for temperature range [-40; 160] °C and supply voltage range [4.5; 5.5] V unless otherwise noted.

#### 8.1. Definitions

This section defines several parameters, which will be used for the magnetic specifications.

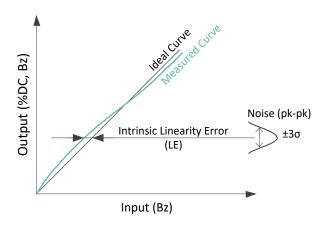

#### 8.1.1. Intrinsic Linearity Error

Figure 7- Sensor accuracy definition

The Illustration of Figure 7 depicts the intrinsic linearity error in new parts. The Intrinsic Linearity Error refers to the IC itself (offset, sensitivity) taking into account an ideal magnetic field. Once associated to a practical magnetic construction and the associated mechanical and magnetic tolerances, the output linearity error increases. However, it can be improved with the multi-point end-user calibration (see chapter 11). As a consequence, this error is typically negligible because it is calibrated away.

#### 8.1.2. Total Drift

After calibration, the output field of the sensor might still change due to temperature change, aging, etc.. This is defined as the total drift  $\partial B_{TT}$ :

$$\partial B_{TT} = \max\{B(B_{IN}, T, t) - B(B_{IN}, T_{RT}, t_0)\}$$

where  $B_{IN}$  is the input field, T is the temperature,  $T_{RT}$  is the room temperature, and t is the elapsed lifetime after calibration.  $t_0$  represents the status at the start of the operating life. Note the total drift  $\partial B_{TT}$  is always defined with respect to field at room temperature. In this datasheet,  $T_{RT}$  is typically defined at 35°C, unless stated otherwise. The total drift is valid for all fields along the full mechanical stroke.

**REVISION 001 - 27-Feb-2020** Page 15 of 58

Datasheet

### 8.2. Magnetic Field Specification for the Sensor Accuracy

The accuracy of the MLX91377 is valid with the external magnetic field specified in the below, and are valid for temperature range [-40; 160] °C unless otherwise noted.

| Parameter                | Symbol | Min   | Тур | Max | Unit   | Condition |

|--------------------------|--------|-------|-----|-----|--------|-----------|

| Magnetic Input Span (11) |        | 10    | 25  | 100 | mT     | Bz        |

| System thermal drift     | TCm    | -3000 |     |     | ppm/°C |           |

Table 11 - Magnetic field specification for the sensor accuracy

### 8.3. Accuracy Specifications

Offset, noise & sensitivity accuracy specifications enable quantification of the system's accuracy. Sensitivity drift is the IC thermal drift and the variation of the magnet drift.

#### 8.3.1. Magnetic Accuracy

Please note the offset and noise are specified referring to the sensor output in Table 12. Therefore the specified values are based on the condition that the gain of the device (parameters GAIN and DIG\_GAIN in Table 20) is properly adjusted to map the magnetic input span and chip output.

| Parameter                                                               | Symbol             | Min | Тур | Max                       | Unit              | Condition                                                                                                                                             |

|-------------------------------------------------------------------------|--------------------|-----|-----|---------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Thermal Output Offset Drift in full temperature range                   | $\Delta^{T}V_{OQ}$ |     |     | 11.2<br>6.0<br>3.9<br>3.0 | LSB <sub>12</sub> | <ul><li>± 10mT magnetic input span</li><li>± 25mT magnetic input span</li><li>± 40mT magnetic input span</li><li>± 80mT magnetic input span</li></ul> |

| Initial Output Offset for room temperature 35°C (12)                    | V <sub>OQ</sub>    |     |     | 10.0                      | LSB <sub>12</sub> | ± 25mT magnetic input span                                                                                                                            |

| Output Noise digital output<br>RMS for room temperature<br>35°C (13)    |                    |     |     | 2.85<br>2.0<br>2.0<br>2.8 | LSB <sub>12</sub> | <ul><li>± 10mT magnetic input span</li><li>± 25mT magnetic input span</li><li>± 40mT magnetic input span</li><li>± 80mT magnetic input span</li></ul> |

| Output Noise analog output<br>RMS for room temperature<br>35°C (13)(14) |                    |     |     | 3.5<br>2.5<br>2.5<br>3.4  | mV                | <ul><li>± 10mT magnetic input span</li><li>± 25mT magnetic input span</li><li>± 40mT magnetic input span</li><li>± 80mT magnetic input span</li></ul> |

<sup>&</sup>lt;sup>11</sup> This parameter indicates the magnetic field span which can be sensed at the device input. This parameter has an unsigned value, i.e. a device with magnetic input span of 10mT can detect a magnetic sensing field from -10mT to 10mT range. This parameter is mapped to the device gain, assuming the full scale of the output is used. For instance, a magnetic input span of 25mT reflects a device gain of 82LSB/mT (digital output) or 0.1V/mT (analog output). Therefore the device should be programmed with a gain which matches the magnetic span. Consequently, the condition for the accuracy specification in section 8.3 will also be changed accordingly.

**REVISION 001 - 27-Feb-2020** Page 16 of 58

<sup>&</sup>lt;sup>12</sup> At time zero.

<sup>&</sup>lt;sup>13</sup> RMS Noise. Valid for no filter.

<sup>&</sup>lt;sup>14</sup> For the analog output, MLX91377 has the flexibility to offer a low noise product version (ASIC) via another product code, at the cost of speed reduction (see the parameter DTI<sub>ANA</sub> in section 7.1 and the parameters in section 7.3). For the detailed performance and ordering information, please contact your Direct Sales Team.

| Parameter                                                               | Symbol        | Min            | Тур | Max                      | Unit              | Condition                                                                                                                                                  |

|-------------------------------------------------------------------------|---------------|----------------|-----|--------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Output Noise digital output<br>RMS in full temperature<br>range (13)    |               |                |     | 4.8<br>2.2<br>2.2<br>3.5 | LSB <sub>12</sub> | <ul><li>± 10mT magnetic input span</li><li>± 25mT magnetic input span</li><li>± 40mT magnetic input span</li><li>± 80mT magnetic input span</li></ul>      |

| Output Noise analog output<br>RMS in full temperature<br>range (13)(14) |               |                |     | 6.0<br>2.7<br>2.7<br>4.3 | mV                | <ul> <li>± 10mT magnetic input span</li> <li>± 25mT magnetic input span</li> <li>± 40mT magnetic input span</li> <li>± 80mT magnetic input span</li> </ul> |

| IC Sensitivity Drift                                                    | $\Delta^{T}S$ | -1.5           |     | 1.5                      | %                 | Related to 35°C                                                                                                                                            |

| Sensitivity Thermal<br>Hysteresis                                       |               | -0.5           |     | 0.5                      | %                 | Temperature cycling will impact sensitivity. Spec is for dry parts.                                                                                        |

| Integral non-linearity (15)                                             | INL           | -0.12<br>-0.25 |     | 0.12<br>0.25             | %                 | 35°C<br>from -40 to 160°C                                                                                                                                  |

| Temperature Sensor<br>Variation <sup>(16)</sup>                         |               | -8<br>-2       |     | 8<br>6                   | °C                | from -40 to 160°C<br>from 35 to 125°C                                                                                                                      |

Table 12 - Magnetic specification for Linear Hall Sensor

**REVISION 001 - 27-Feb-2020** Page 17 of 58

<sup>&</sup>lt;sup>15</sup> Before end user calibration, measured at magnet span ±25mT, with 1mT resolution.

<sup>&</sup>lt;sup>16</sup> Part to part variation of the temperature sensor

# 9. Memory Specifications

| Parameter | Symbol    | Min | Тур  | Max | Unit | Note                                                         |

|-----------|-----------|-----|------|-----|------|--------------------------------------------------------------|

| ROM       | ROMsize   |     | 32   |     | КВ   | 1 bit parity check (single error detection)                  |

| RAM       | RAMsize   |     | 1024 |     | В    | 1 bit parity check (single error detection)                  |

| NVRAM     | NVRAMsize |     | 256  |     | В    | 6 bits ECC (single error correction, double error detection) |

Table 13 - Memory Specifications

**REVISION 001 - 27-Feb-2020** Page 18 of 58

# 10. Output Characteristic and Accuracy

### 10.1. Analog Output

| Parameter                   | Symbol           | Min. | Тур. | Max.       | Unit              | Condition                                                            |

|-----------------------------|------------------|------|------|------------|-------------------|----------------------------------------------------------------------|

| Thermal analog output Drift |                  |      |      | 0.2<br>0.3 | %VDD              | up to 125°C<br>up to 160°C                                           |

|                             |                  |      | 12   |            | bit               | 12bit DAC (Theoretical)                                              |

| Analog Output Resolution    | R <sub>DAC</sub> | -4   |      | +4         | LSB <sub>12</sub> | INL (before EoL calibration),<br>output clamped between 3-<br>97%VDD |

|                             |                  | 0.05 | 1    | 3          | LSB <sub>12</sub> | DNL                                                                  |

| Ratiometric Error           |                  | -0.1 |      | 0.1        | %VDD              |                                                                      |

Table 14 – Analog output accuracy

### 10.2. Digital Output

#### 10.2.1. General Definition

The MLX91377 provides a digital output signal compliant with SAE J2716 Revised APR2016.

By default, the MLX91377 outputs the SPC (Short PWM Code). It is an extension of the SAE J2716 SENT protocol. It allows on-demand transmission of one data frame where the master triggers the transfer of data. The transmission of the SPC frame is always triggered by the master in every mode (synchronous and with ID selection). Both modes are described further in this chapter.

Optionally, the MLX91377 supports also the typical SENT revision 2016 (SAE J2716 APR2016) and compatible to the previous revisions <sup>(17)</sup>.

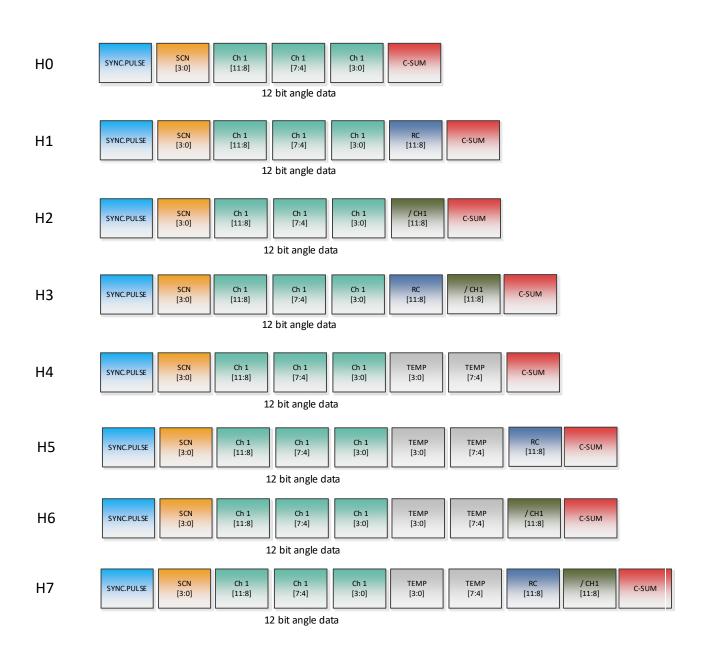

The digital output of the MLX91377 transmits a sequence of data nibbles, according to the following configurations:

| Description                     | Symbol   | Min | Тур                 | Max | Unit  | Description                                                                                                              |

|---------------------------------|----------|-----|---------------------|-----|-------|--------------------------------------------------------------------------------------------------------------------------|

| Clock tick time                 | tickTime | 0.5 | 1.5 <sup>(17)</sup> | 12  | μs    | Main use cases:  SPC, 1.5µs tick time (default)  Normal SENT, 3µs tick time  Slow SENT, 6µs tick time  (see section 7.4) |

| Number of data nibbles          | Xdn      | 3   |                     | 6   |       |                                                                                                                          |

| Frame duration (no pause pulse) | Npp      | 154 |                     | 270 | ticks | 6 data nibbles                                                                                                           |

<sup>&</sup>lt;sup>17</sup> Please contact our Direct Sales Team if other options then main use cases is required.

**REVISION 001 - 27-Feb-2020** Page 19 of 58

Datasheet

| Description                     | Symbol | Min | Тур | Max | Unit  | Description           |

|---------------------------------|--------|-----|-----|-----|-------|-----------------------|

| Frame duration with pause pulse | Ррс    | 282 | 320 | 922 | ticks |                       |

| Sensor type                     | A.3    |     |     |     |       | Single Secure sensors |

Table 15 - SENT Protocol Frame Definition

#### 10.2.2. Tick Time requirements

The basic SPC protocol unit time is defined as 3  $\mu$ s. The protocol standard requires a tick time variation of no more than 20% for legacy applications and 10% for general applications. The lowest tick time that can be programmed in the MLX91377 is 0.5  $\mu$ s. Improved Emission Mode will only be possible for tick time equal or greater to 1.5  $\mu$ s.

### 10.2.3. Output Configuration

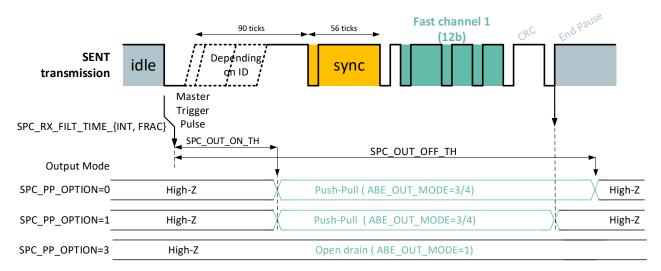

In SPC mode, the MLX91377 can be configured in open drain mode, normal push-pull mode, as well as an enhanced emission mode, see also section 13.1.1.

The default output driver configuration is to send the SENT frame in push-pull mode.

Users can select three options (see parameter SPC\_PP\_Option, Table 20 in chapter 11):

- 1. IC is always in open drain

- 2. IC sends the SENT frame from a pre-defined timer (SPC\_OUT\_ON\_TH) to CRC in push-pull. It then returns to high-Z

- 3. IC sends the SENT frame from a pre-defined timer (SPC\_OUT\_ON\_TH) until end of a pre-defined timer (SPC\_OUT\_OFF\_TH). It then returns to high-Z.

Figure 8 – SPC output driver state switching

| Parameter          | Symbol          | Min | Тур | Max | Unit | Condition                                                                                  |

|--------------------|-----------------|-----|-----|-----|------|--------------------------------------------------------------------------------------------|

| Push-Pull Duration | $T_{push-pull}$ | 280 |     | 550 | μs   | Configurable Duration how long IC stays in push-pull once sync pulse of SENT frame starts. |

Table 16: Push-pull duration in SPC mode

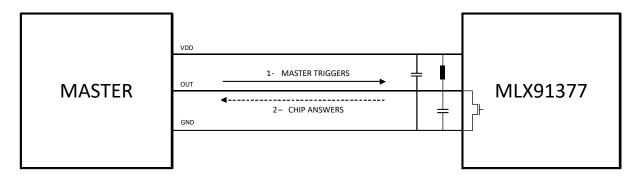

The sensor output driver can also be configured as open-drain to enable the master to drive the line. Initially the line is at high level, the chip is waiting for the master to pull it low. This state is called 'Idle

**REVISION 001 - 27-Feb-2020** Page 20 of 58

Datasheet

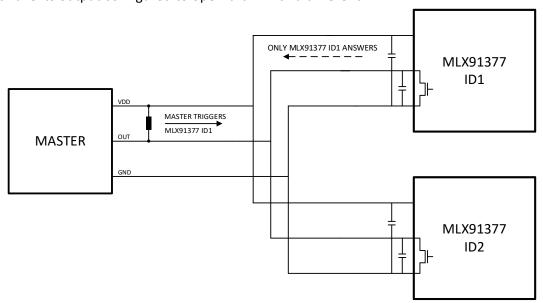

state', meaning the sensor is not transmitting any data. At a given time, the master will send a trigger low pulse along the line. The embedded CPU of the sensor will measure this master pulse length. If it is recognized as a valid trigger, the chip will answer by sending back an SPC frame containing the current data. Several configurations of the SPC frame are available. If the trigger pulse is not valid, the chip will not transmit any data, keeping the line free.

Figure 9 – SPC standard master-slave configuration

Like in SENT, the tick time is the unit reference for SPC. It can be as low as  $0.5\mu$ s enabling fast transmission rate and short frames. However, the default tick time value is  $1.5\mu$ s in SPC mode, to benefit from the fast acquisition and magnetic processing of the device.

For the MLX91377, the output resistance, e.g. the external pull-up or pull-down resistor should be carefully selected, because the MLX91377 has a built-in high order low pass filter, too heavy resistive load will deteriorate the generated SPC signal, and could make the output signal not comply to the SPC specifications, such as the fall times and the minimum output voltages, i.e. parameters  $V_{\text{satD\_hije}}$  and  $V_{\text{satD\_hije}}$  in Table 7 in chapter 6. In principle, the values in Table 7 in chapter 6 should be considered, which means it is not recommended to have a resistive load value smaller than  $10k\Omega$ , and a resistive load value smaller than  $3k\Omega$  should be avoided. The maximum output resistive load value should be less than  $55k\Omega$  to avoid unexpected impact from leakage current.

Furthermore, the output capacitance should also be properly chosen together with the output resistive load to correspondingly match the application, e.g. tick time, SPC ID, etc. to allow appropriate time window for the trigger pulse reception. The worst case scenario occurs for SPC ID0, where the trigger pulse should be recognized within only 4 ticks (refer to Table 19 and Figure 14 in section 0), resulting in 6  $\mu$ s time window for 1.5  $\mu$ s tick time SPC protocol. Therefore, RC time constant should be less than 6  $\mu$ s in such application. When the time window for the trigger pulse reception changes, the resistive and capacitive load on output can be scaled correspondingly. It is also important to note that the mentioned capacitive load refers to the total load on the bus, meaning the value should be equally divided if there are multiple sensors connected, also the load on the ECU side should be taken into account and scaled properly.

#### 10.2.4. Frame Content

#### 10.2.4.1. Global Definition

A message frame consists of the following sequence:

- Trigger pulse

- 2. Synchronization pulse

- 3. Status and communication nibble

**REVISION 001 - 27-Feb-2020** Page 21 of 58

Datasheet

- 4. Data nibbles

- 5. Checksum nibble

- 6. End Lone pulse

The overall scheme of the SPC frame transmission is described in the following figure.

Figure 10 - SPC Frame description

#### 10.2.4.2. Trigger Pulse

The trigger pulse is considered to be part of the SPC frame. The timing related to this trigger pulse is critical as it is initializing the data transfer. The sensor is monitoring the line and computes the duration the line is kept low by the master. This time is called "master low time".

| Parameter              | Symbol       | Min  | Тур  | Max | Unit |

|------------------------|--------------|------|------|-----|------|

| Falling edge threshold | $V_{thfSPC}$ | 1.1  | 1.32 | 1.7 | V    |

| Rising Edge Threshold  | $V_{thrSPC}$ | 1.25 | 1.52 | 1.8 | V    |

Table 17 – SPC Master Trigger Pulse Specifications

The falling edge of the trigger pulse is considered to be the reference of the protocol. The master low time is quantized using clock ticks.

After a non-valid trigger detected, a blanking time of five unit times (counted from the detected rising edge of the trigger pulse) is used by the sensor, before the next trigger measurement is performed. This concept improves EMC robustness and avoids unwanted answer from the chip if the line is subject to spikes.

After detection of a valid trigger and expiration of the trigger pulse time according to the selected transmission mode the sensor starts with the remaining protocol frame.

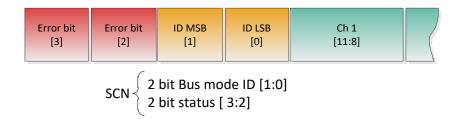

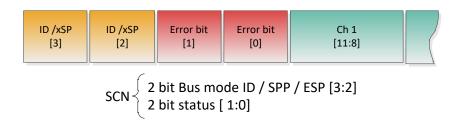

#### 10.2.4.3. Status and communication nibble (SCN)

The status nibble contains information for error reporting and some optional information like the chip ID or slow channel data.

**REVISION 001 - 27-Feb-2020** Page 22 of 58

Datasheet

The position of the 2 status bits and 2 ID bits in SPC mode of MLX91377 complies with the one specified in the SPC standard, but can be reversed if the SENT-standard definition is preferred.

Figure 11 – SPC Bus Transmission Mode Multiplex Example (SPC SCN BIT ORDER=1)

Figure 12 – SENT Transmission Mode Multiplex Example (SPC\_SCN\_BIT\_ORDER=0)

#### 10.2.4.4. Data Nibble

The definition of the data nibbles in SPC matches with SENT. The number of data nibbles transmitted is determined by frame format configured. The data content is programmable. By default, 12 bits of data are transmitted in 3 nibbles.

#### 10.2.4.5. Checksum Nibble

SPC protocol allows transmission of error/warning flags in the status and communication nibble. Then it is highly recommended to take this nibble into the checksum calculation. This option is programmable in the MLX91377. Nevertheless, to be SENT compatible, it is possible to limit the checksum input data to data nibbles only.

MLX91377 also supports the SPC improved nibble checksum algorithms (for the SENT nibbles), method-E and method-O.

#### 10.2.4.6. End Lone Pulse

The MLX91377 generates a pulse with a length of 12 clock ticks after transmission of checksum nibble. In that case the master cannot trigger the chip. During that period, MLX91377 is still holding the line. The blanking time is programmable, see parameters SPC\_OUT\_ON\_TH, SPC\_OUT\_OFF\_TH in chapter 11.

#### 10.2.5. Synchronous Transmission Mode

In the SPC synchronous mode, the sensor responds to a low pulse of duration between 1.5 and 4 tick times. The SENT data frame shall be transmitted with a delay of 10 tick times such that the allowed total

**REVISION 001 - 27-Feb-2020** Page 23 of 58

trigger time range specified in Table 18 is met. This configuration ensures synchronisation between the master and the chip, and the data gets acquired in the same frame.

| Parameter                             | Symbol              | Min  | Тур  | Max  | Unit  |

|---------------------------------------|---------------------|------|------|------|-------|

| SPC Synchronous Mode Trigger Low Time | $t_{mlowSPC}$       | 1.5  | 2.75 | 4    | ticks |

| Total trigger time                    | t <sub>mtrSPC</sub> | 10.8 | 13.5 | 16.3 | ticks |

Table 18 – SPC Synchronous Timings

#### 10.2.6. Bus Transmission Mode

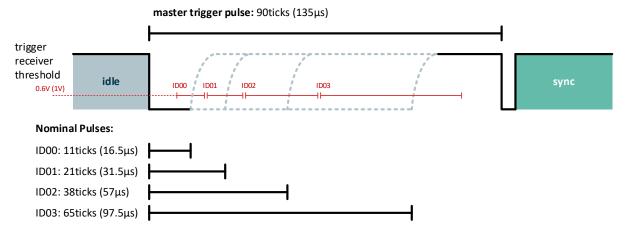

In the on-demand timing modes, the sensor responds to SPC trigger pulses from the master when its low pulse time corresponds to its pre-programmed ID. The selection of the ID is done with the parameter SPC\_ID.

| Parameter                            | Symbol              | SPC_CHIP_ID | Min | Тур | Max   | Unit  | Remark                                                        |

|--------------------------------------|---------------------|-------------|-----|-----|-------|-------|---------------------------------------------------------------|

|                                      |                     | 0           | 8   |     | 15    | ticks |                                                               |

| Bus Mode                             |                     | 1           | 16  |     | 28    | ticks |                                                               |

| Master Low t <sub>mlowSPC</sub> Time | 2                   | 29          |     | 49  | ticks |       |                                                               |

|                                      |                     | 3           | 50  |     | 82    | ticks |                                                               |

| Total trigger<br>time                | t <sub>mtrSPC</sub> | -           | -   | 90  | -     | ticks | master trigger pulse, independent of SPC_ID, not programmable |

Table 19 – Bus Transmission Mode Timings

The ECU is able to trigger only one chip on a bus. The maximum amount of chip on the bus line is 4. Each chip must have its output configured to open-drain with a different ID.

Figure 13 – SPC Bus Transmission Mode Multiplex Example

Figure 14 shows the timing diagram of the trigger pulse reception depending on the SPC ID.

**REVISION 001 - 27-Feb-2020** Page 24 of 58

Datasheet

Figure 14 – Time Window for the Trigger Pulse Reception

#### Notes:

- ID01 and ID03 are advised when only 2 sensors are on the bus

- For correct trigger pulse reception, the clock tolerance of the sensor, the time constant of the rising edge and the receiver threshold shall be considered

- The ECU may adjust the low trigger time to account for the time constant of the rising edge

- Example timings are calculated for the default 1.5µs tick time

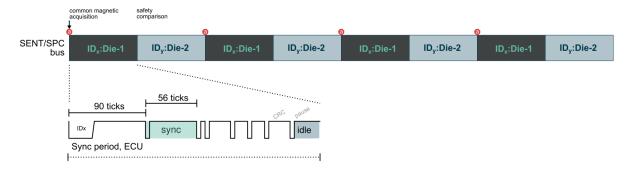

Bus Transmission Mode allows two configurations for acquiring data and sending data:

- 1. The IC for which SPC ID matches acquires its data and sends in the same frame the data.

- 2. All IC's on the bus acquire the data when a specific SPC ID is sent. Each IC buffers and transmits when called upon, see Figure 15.

Figure 15 – Acquire Data during one SPC ID on all ICs on the same bus. Buffer and send when SPC ID matches.

**REVISION 001 - 27-Feb-2020** Page 25 of 58

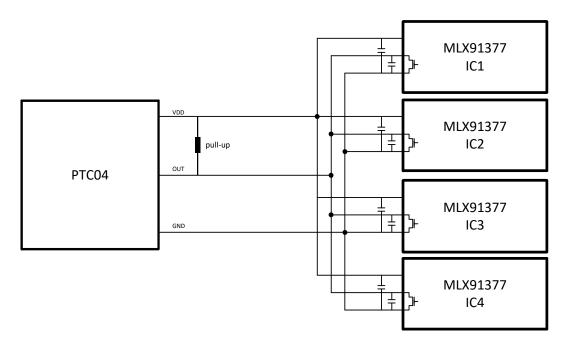

#### 10.2.7. Programming in Bus Mode

The EoL programming can be executed even if 4 chips are connected to the same bus. The protocol is capable of selective communication with one chip connected in bus configuration together with other chips (up to 4 on the same line). It uses the MUPET\_ADDRESS stored in NVRAM to select the chip to be programmed. When programming 4 chips in parallel, external serial resistors shall be avoided, and are in fact not needed, as the improved emission mode is addressing the additional filtering via a resistance implemented on chip. It enables EoL programming even if 4 chips are connected to the same bus. The SPC ID must be programmed up front. Discuss with your local sales representative for this option.

Figure 16 – Example of multiple units programming

**REVISION 001 - 27-Feb-2020** Page 26 of 58

# 11. End-User Programmable Items

| Parameter                                   | Description                                                                                                                                                                                                            | Defa                          | ault Value | es    |

|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|------------|-------|

| raiailletei                                 | Description                                                                                                                                                                                                            | SPC A                         | nalog #    | #bits |

|                                             | GENERAL CONFIGURATION                                                                                                                                                                                                  |                               |            |       |

| USER_ID[05]                                 | User Id. Reference, details see Table 21 in chapter 12                                                                                                                                                                 | see Table 21 in<br>chapter 12 |            | 8     |

| WARM_TRIGGER_LONG                           | Add delay for PTC Entry Level                                                                                                                                                                                          | 0                             | 0          | 1     |

| WARM_ACT_HIGHV                              | Select PTC Entry Level Default 0 = V <sub>PROVO</sub>                                                                                                                                                                  | 0                             | 0          | 1     |

| ROUT_LOW                                    | Select output impedance for PTC communication                                                                                                                                                                          | 1                             | 1          | 1     |

| MUPET_ADDRESS_MODE                          | Configuration for PTC address. Do not modify!                                                                                                                                                                          | 0                             | 0          | 1     |

| MUPET_ADDRESS                               | PTC address for which the slave will communicate                                                                                                                                                                       | 0/1                           | 0/1        | 2     |

| MEMLOCK                                     | Enable NVRAM write protection                                                                                                                                                                                          | 0                             | 0          | 2     |

|                                             | SENSOR FRONT END                                                                                                                                                                                                       |                               |            |       |

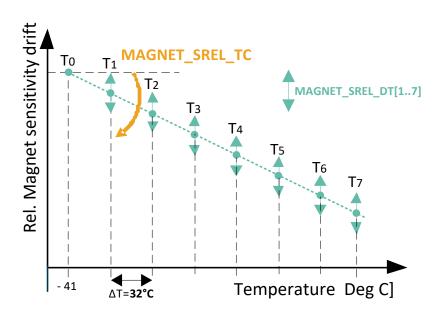

| MAGNET_SREL_TC                              | Linear magnet TC correction: -1525ppm/(°C * 100LSB)                                                                                                                                                                    | 0                             | 0          | 8     |

| MAGNET_SREL_DT [17]                         | Piecewise linear magnet TC correction, delta vs Linear magnet TC correction (MAGNET_SREL_TC)                                                                                                                           | 0                             | 0          | 8     |

| GAIN                                        | Analog Virtual gain code [ 063]                                                                                                                                                                                        | 29                            | 29         | 8     |

| SENSING_MODE                                | Sensing mode: Bz = Fixed for Linear Hall application                                                                                                                                                                   | 7                             | 7          | 3     |

|                                             | FILTERING                                                                                                                                                                                                              |                               |            |       |

| FILTER                                      | FIR filter bandwidth selection                                                                                                                                                                                         | 0                             | 0          | 2     |

| HYST                                        | Hysteresis of the denoising filter (hides the small variations but lowers the resolution) Denoising and FIR filtering are applied before the linearization step.                                                       | 0                             | 0          | 8     |

| DENOISING_FILTER_ALPHA_<br>SEL              | Select the alpha parameter of the EMA (IIR) filter                                                                                                                                                                     | 0                             | 0          | 2     |

| SPC_RX_FILT_TIME_INT SPC_RX_FILT_TIME_FRACT | Filtered SPC trigger pulse: Min pulse tick time = ( 8* SPC_RX_FILT_TIME_INT + SPC_RX_FILT_TIME_FRACT)/8                                                                                                                | 6<br>0                        | N/A        | 4     |

| SPC_BLANKING_TIME                           | SPC blanking time (= 5+2*SPC_BLANKING_TIME tick) in case of invalid SPC -ID pulse detected, counted from the rising edge of the trigger pulse. Any other (parasitic) pulse occurring during that time will be ignored. | 0                             | N/A        | 2     |

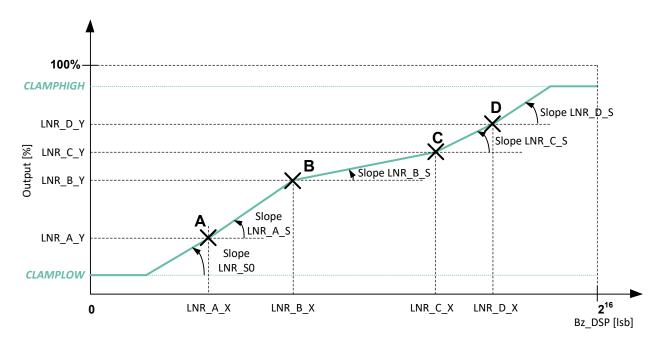

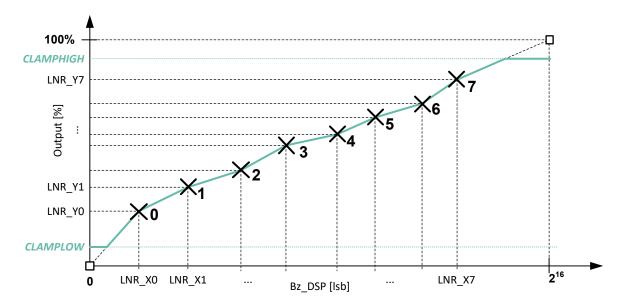

| LINEAR TRANSFER CHARACTERISTIC              |                                                                                                                                                                                                                        |                               |            |       |

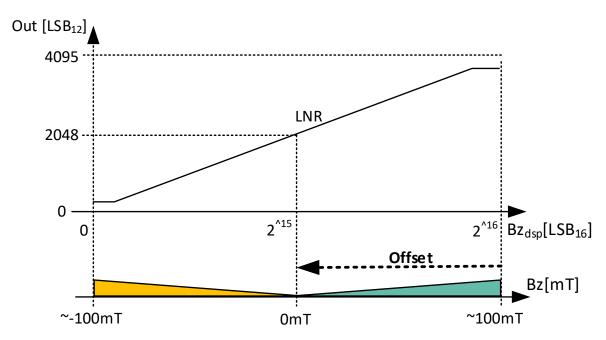

| OFFSET                                      | Quiescent position for PWL linearization, default 50%                                                                                                                                                                  | 32768                         | 32768      | 16    |

| Polarity                                    | Enable reverse output polarity selection                                                                                                                                                                               | 0                             | 0          | 1     |

| 4POINTS                                     | Enable 4 points PWL linearization                                                                                                                                                                                      | 0                             | 0          | 1     |

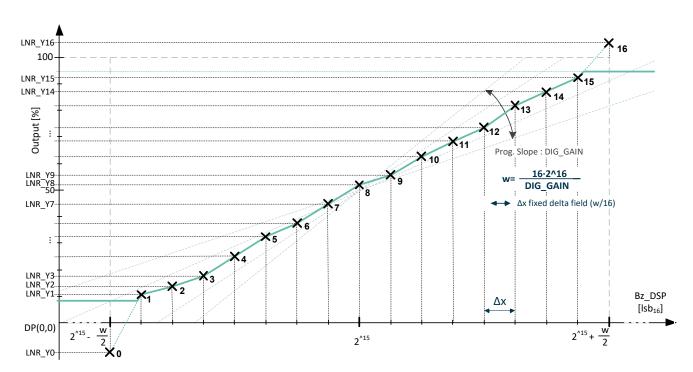

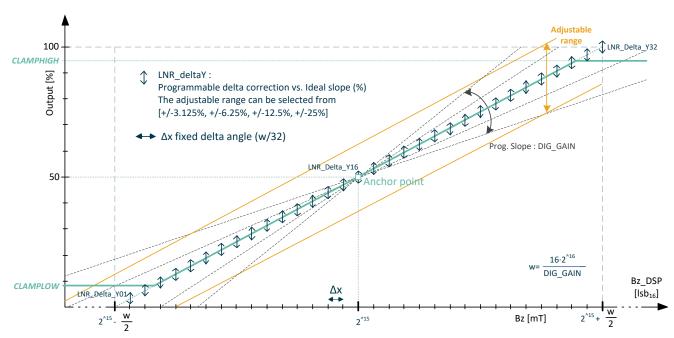

| DSP_LNR_RESX2                               | Enable a doubled LNR method  0: 4-points or 16-segments  1: 8-points or 32-segments                                                                                                                                    | 0                             | 0          | 1     |

**REVISION 001 - 27-Feb-2020** Page 27 of 58

Datasheet

|                                       | INSPIRED ENGINEER                                            |        |             |      |

|---------------------------------------|--------------------------------------------------------------|--------|-------------|------|

| Parameter                             | Description                                                  |        | ault Values | its  |

|                                       | Post DSP Gain stage, input range for PWL linearization       | JFC A  | ilaiog #L   | )ILS |

| DIG_GAIN                              | FS: +/- 2^15 *16/DIG_GAIN [ typ +/- 100 mT *16/<br>DIG_GAIN] | 16     | 16          | 8    |

| GAIN_ANCHOR_MID                       | Select 50% position as anchor point Post DSP Gain stage      | 1      | 1           | 1    |

| USEROPTION_SCALING                    | Enables output scaling x2<br>0 = [0100%]<br>1 = [-50%150%]   | 1      | 1           | 1    |

| LNR_S0                                | 4-pts – Slope coefficient before reference point A           | N/A    | N/A         | 16   |

| LNR_A_X, LNR_B_X,<br>LNR_C_X, LNR_D_X | 4-pts - X coordinate for reference points A,B,C,D            | N/A    | N/A         | 16   |

| LNR_A_Y, LNR_B_Y,<br>LNR_C_Y, LNR_D_Y | 4-pts - Y coordinate for reference points A,B,C,D            | N/A    | N/A         | 16   |

| LNR_A_S, LNR_B_S,<br>LNR_C_S, LNR_D_S | 4-pts – Slope coefficient for reference points A,B,C,D       | N/A    | N/A         | 16   |

| LNR_Y00                               | 8-pts / 16 segments - Y coordinate point 0                   | 0x4009 | 0x4CCD      | 16   |

| LNR_Y01                               | 8-pts / 16 segments - Y coordinate point 1                   | 0x4804 | 0x5334      | 16   |

| LNR_Y02                               | 8-pts / 16 segments - Y coordinate point 2                   | 0x5000 | 0x599A      | 16   |

| LNR_Y03                               | 8-pts / 16 segments - Y coordinate point 3                   | 0x57FC | 0x6000      | 16   |

| LNR_Y04                               | 8-pts / 16 segments - Y coordinate point 4                   | 0x5FF8 | 0x6667      | 16   |

| LNR_Y05                               | 8-pts / 16 segments - Y coordinate point 5                   | 0x67F4 | 0x6CCD      | 16   |

| LNR_Y06                               | 8-pts / 16 segments - Y coordinate point 6                   | 0x6FF0 | 0x7334      | 16   |

| LNR_Y07                               | 8-pts / 16 segments - Y coordinate point 7                   | 0x77EC | 0x799A      | 16   |

| LNR_Y08                               | 8-pts / 16 segments - Y coordinate point 8                   | 0x7FE8 | 0x8000      | 16   |

| LNR_Y09                               | 8-pts / 16 segments - Y coordinate point 9                   | 0x87E4 | 0x8667      | 16   |

| LNR_Y10                               | 8-pts / 16 segments - Y coordinate point 10                  | 0x8FE0 | 0x8CCD      | 16   |

| LNR_Y11                               | 8-pts / 16 segments - Y coordinate point 11                  | 0x97DC | 0x9333      | 16   |

| LNR_Y12                               | 8-pts / 16 segments - Y coordinate point 12                  | 0x9FD8 | 0x999A      | 16   |

| LNR_Y13                               | 8-pts / 16 segments - Y coordinate point 13                  | 0xA7D4 | 0xA000      | 16   |

| LNR_Y14                               | 8-pts / 16 segments - Y coordinate point 14                  | 0xAFD0 | 0xA667      | 16   |

| LNR_Y15                               | 8-pts / 16 segments - Y coordinate point 15                  | 0xB7CC | 0xACCD      | 16   |

| LNR_Y16                               | 8-pts / 16 segments - Y coordinate point 16                  | 0xBFC8 | 0xB333      | 16   |

| LNR_X[0007]                           | 8-pts - X coordinate point 07                                | N/A    | N/A         | 16   |

| LNN_DELTA_Y[0032]                     | 32 segments - Delta Y coordinate point 032                   | N/A    | N/A         | 8    |

| LNR_DELTA_Y_EXPAND_LO<br>G2           | Adjust the span of 32 segments NV_LNR_DELTA_Y{n} offsets     | 0      | 0           | 2    |

| CLAMPLOW                              | Low clamping value of field data                             | 16     | 32767       | 16   |

| CLAMPHIGH                             | High clamping value of field data                            | 65408  | 32767       | 16   |

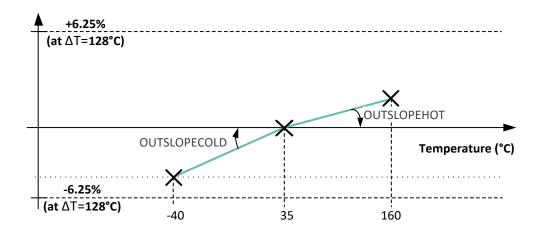

| OUTSLOPE_SEL                          | Possible output offset correction within the post-DSP chain: | 0      | 0           | 2    |

| Parameter                  | Description                                                                                                                                     |       | ault Valu | es    |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------|-------|

| raiametei                  |                                                                                                                                                 | SPC A | nalog     | #bits |

|                            | O: disabled (default)  1: enabled, applied after discontinuity point stage  2: enabled, applied before clamping stage  3: disabled (unused)     |       |           |       |

| OUTSLOPE_COLD              | Slope coefficient at cold of the programmable temperature-dependent offset. Used only if NV_OUTSLOPE_SEL enabled                                | 0     | 0         | 8     |

| OUTSLOPE_HOT               | Slope coefficient at hot of the programmable temperature-dependent offset. Used only if NV_OUTSLOPE_SEL enabled                                 | 0     | 0         | 8     |

|                            | DIAGNOSTICS                                                                                                                                     |       |           |       |

| DIAG_GLOBAL_EN             | Diagnostics global enable. <b>Do not modify!</b> (see section 14.2 Safety Mechanisms)                                                           | 1     | 1         | 1     |

| DIAG_TEMP_THR_LOW          | Temperature threshold & limiter for lower-temperature diagnostic. Default=08 -> -57 deg.C                                                       | 8     | 8         | 8     |

| DIAG_TEMP_THR_HIGH         | Temperature threshold & limiter for over-temperature diagnostic. Default=128 -> 183 deg.C                                                       | 128   | 128       | 8     |

| DIAG_FIELDTOOHIGHTHRES     | Field strength limit over which a fault is reported. (see 13.5.4)                                                                               | 255   | 255       | 8     |